El

muestreador retentor

Definición

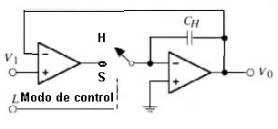

El amplificador muestreador y retentor, es un circuito que opera como

un amplificador cuando está en modo de muestreo, pero en modo de retención su

salida es idealmente constante, independiente de la entrada, siendo este valor

constante, él que existía en la entrada en el momento de pasar del modo de

muestreo al modo de retención. El cambio de modo se controla a través de una señal digital, la cual actúa sobre un

interruptor. En la figura se muestra un circuito amplificador muestreador y

retentor de ganancia unitaria.

La operación de este

circuito está determinada por dos modos

de funcionamiento: modo de muestreo y modo de retención.

Modo de muestreo: con el

interruptor S cerrado, la tensión de salida VO en el capacitor CH

sigue a la señal de entrada V1.

Modo de retención: en este modo el

interruptor S se abre y al tensión de

salida VO es en condiciones ideales, igual a la que existía a la

entrada en el momento de apertura del interruptor.

Las características más

importantes del amplificador muestreador y retentor son las siguientes:

1. El tiempo de adquisición, es el tiempo requerido para que la salida

del muestreador retentor alcance su valor final (dentro de una banda de error)

después de pasar del modo de retención al modo de muestreo. Esto incluye el

retardo del interruptor en actuar, el tiempo de cambio y el tiempo de

estabilización del amplificador. El tiempo de adquisición es reducido,

disminuyendo el valor del capacitor de retención CH.

2. El retardo en la apertura, es el tiempo requerido por el interruptor

para abrir completamente después de pasar del modo de muestreo al modo de

retención.

3. La transferencia de carga, es el voltaje que aparece en la salida del

muestreador, producto de la carga transferida al capacitor de retención CH,

vía capacitancias parásitas, cuando está en el modo de retención.

4. La caída, es el cambio en el voltaje de salida del muestreador mientras está en modo de retención debido a

la descarga del capacitor de retención CH.

5. El tiempo de estabilización, es el tiempo requerido para que la salida

del muestreador y retentor alcance su valor (dentro de una banda de error

especificada), después de pasar del modo de muestreo al modo de retención.

En la figura se pueden apreciar estas características, al actuar un amplificador muestreador y retentor sobre una señal de forma arbitraria.